# INTEGRATED CIRCUITS

# DATA SHEET

# **P90CE201**16-bit microcontroller

Product specification

File under Integrated Circuits, IC21

August 1993

# 16-bit microcontroller

# P90CE201

#### **CONTENTS**

| 1          | FEATURES                                                                   | 10           | 8-BIT GENERAL PORT                               |

|------------|----------------------------------------------------------------------------|--------------|--------------------------------------------------|

| 2          | GENERAL DESCRIPTION                                                        | 10.1         | 8-bit General Port registers                     |

| 3          | ORDERING INFORMATION                                                       | 11           | 8-BIT AUXILIARY PORT                             |

| 4          | PINNING INFORMATION                                                        | 11.1         | 8-bit Auxiliary Port registers                   |

| 4.1        | Pinning                                                                    | 12           | WATCHDOG TIMER                                   |

| 4.2        | Pin description                                                            | 13           | TIMERS                                           |

| 5          | CPU FUNCTIONAL DESCRIPTION                                                 | 13.1         | General                                          |

| 5.1        | General                                                                    | 13.2         | Timer operating modes                            |

| 5.2        | 5.2 Programming model and data organization                                | 13.3         | Timer registers                                  |

| 5.3<br>5.4 | Internal and external operation Processing states and exception processing | 14           | ELECTROMAGNETIC COMPATIBILITY (EMC) IMPROVEMENTS |

| 5.5<br>5.6 | Stack format CPU interrupt processing                                      | 15           | ELECTRICAL SPECIFICATIONS                        |

| 6          | SYSTEM CONTROL                                                             | 15.1<br>15.2 | Limiting values DC Characteristics               |

| 6.1        | Memory mapping                                                             | 15.3         | AC Characteristics                               |

| 6.2<br>6.3 | Interrupt controller System Control Registers                              | 16           | REGISTER MAP                                     |

| 6.4        | Reset                                                                      | 17           | PACKAGE OUTLINE                                  |

| 6.5        | Clock circuitry                                                            | 18           | SOLDERING                                        |

| 7          | INSTRUCTION SET                                                            | 18.1         | Introduction                                     |

| 7.1        | Addressing modes                                                           | 18.2         | Reflow soldering                                 |

| 7.2        | Instruction timing                                                         | 18.3         | Wave soldering                                   |

| 8          | I <sup>2</sup> C-BUS INTERFACE                                             | 18.4         | Repairing soldered joints                        |

| 8.1        | General                                                                    | 19           | DEFINITIONS                                      |

| 8.2        | I <sup>2</sup> C-bus interface registers                                   | 20           | LIFE SUPPORT APPLICATIONS                        |

| 9          | UART SERIAL INTERFACE                                                      | 21           | PURCHASE OF PHILIPS I <sup>2</sup> C COMPONENTS  |

| 9.1        | General                                                                    |              |                                                  |

| 9.2<br>9.3 | Operating modes UART registers                                             |              |                                                  |

## 16-bit microcontroller

P90CE201

#### 1 FEATURES

- · CMOS technology

- Full 68000 software compatibility

- · 32-bit internal structure

- 16-bit internal data transfer

- 8-bit access to external ROM/RAM

- External addressing range 16 Mbytes for ROM and 16 Mbytes for RAM

- Unused address pins can be used as quasi-bidirectional ports

- On-chip address decoder for ROM/RAM

- 8 edge triggered programmable interrupts that can also be used as quasi-bidirectional ports

- Reset control

- Built-in clock generator

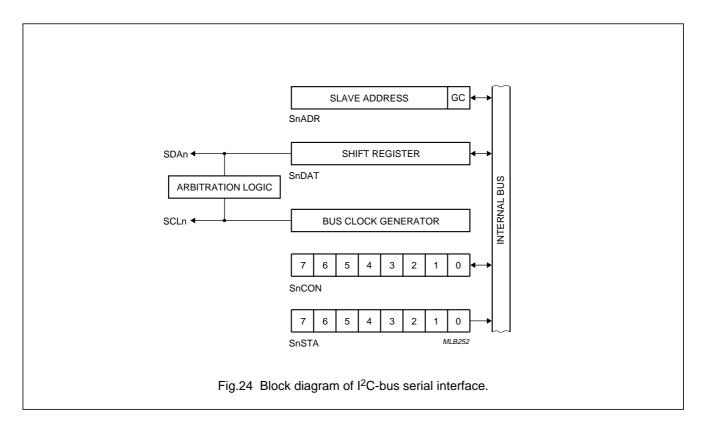

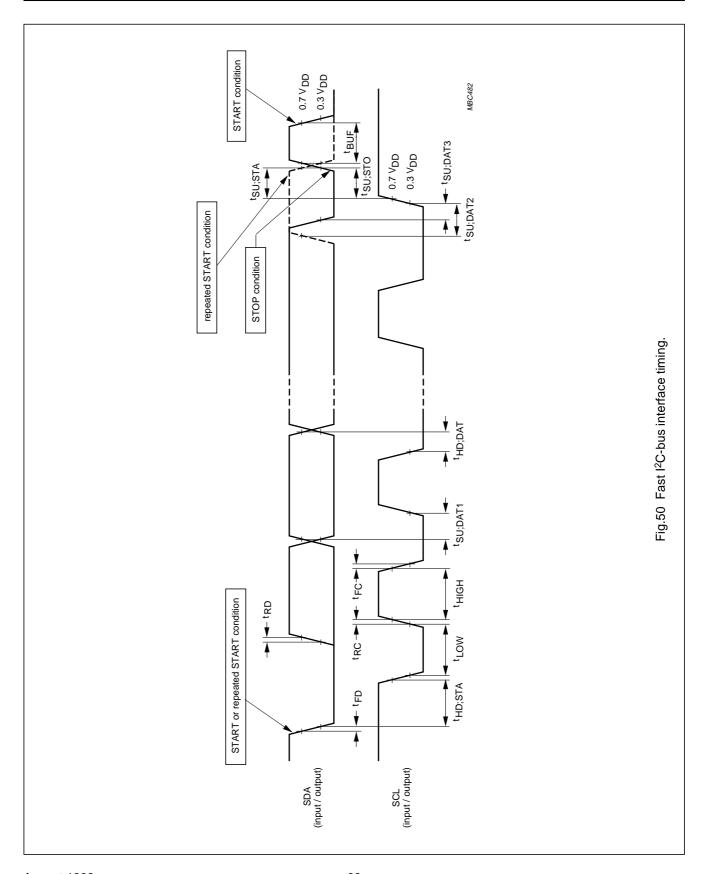

- 2 fully independent fast I<sup>2</sup>C-bus serial interfaces

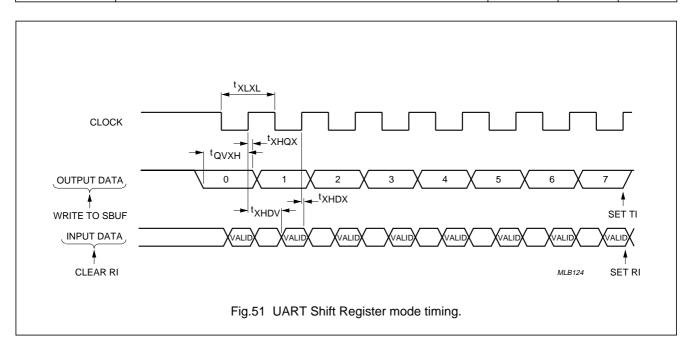

- UART serial interface (4 modes)

- 3 fully independent 16-bit timers

- · Watchdog timer

- 8-bit quasi-bidirectional port, 4-bits with high drive capability

- · EMC optimized layout and pinning

- 64-pin QFP package

#### 2 GENERAL DESCRIPTION

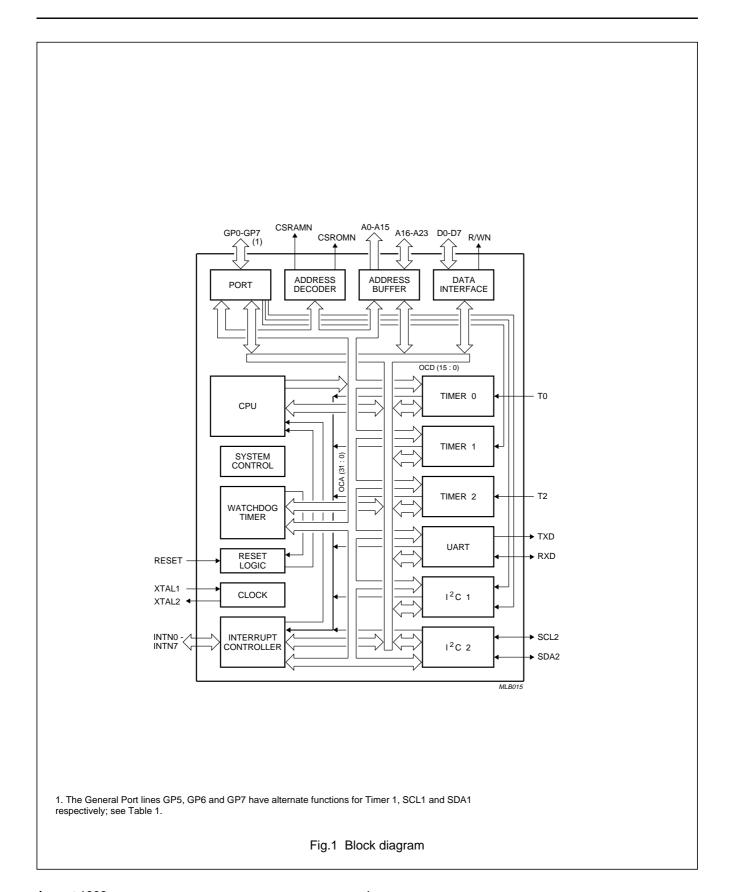

The P90CE201 is a member of the P9XCXXX family of highly integrated 16-bit microcontrollers for use in a wide variety of applications. It is fully software compatible with the 68070/68000. The complete set of system functions available on the chip results in reduced system cost. Additionally, its modular design concept permits future extension to the family.

#### 3 ORDERING INFORMATION

| EXTENDED    |      | PAC          | KAGE     | CLOCK                 | TEMPERATURE RANGE  |           |

|-------------|------|--------------|----------|-----------------------|--------------------|-----------|

| TYPE NUMBER | PINS | PIN POSITION | MATERIAL | CODE                  | FREQUENCY<br>(MHz) | (°C)      |

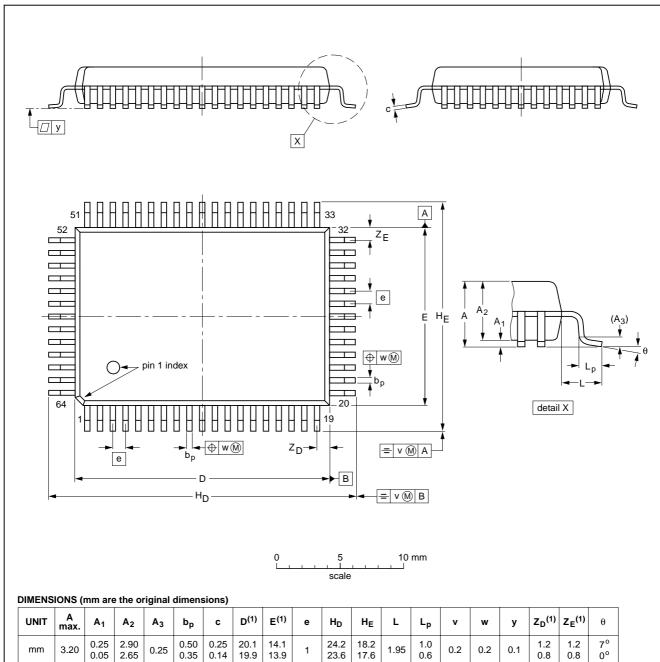

| P90CE201AEB | 64   | QFP          | plastic  | SOT319 <sup>(1)</sup> | 24.0               | -25 to 85 |

#### Note

1. SOT319-2; 1996 November 28.

# 16-bit microcontroller

# P90CE201

# 16-bit microcontroller

P90CE201

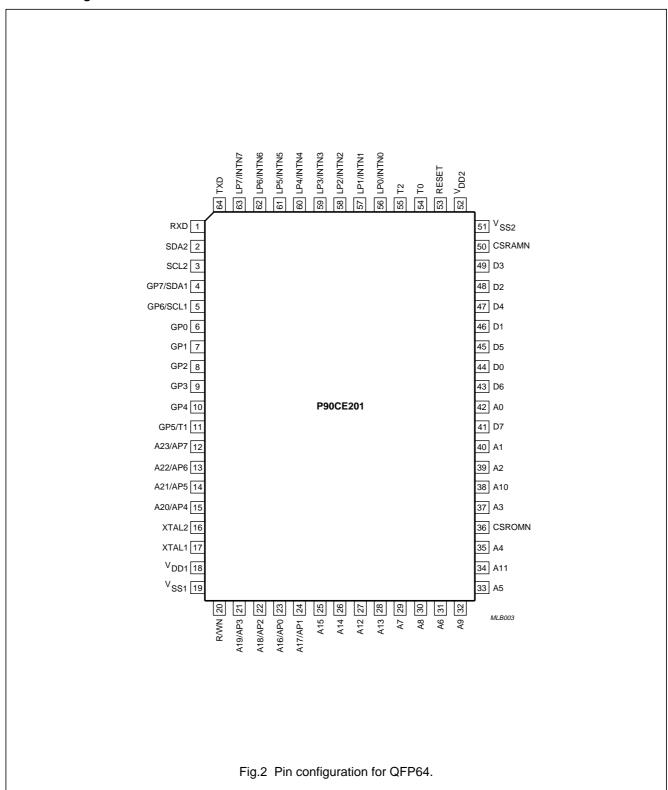

#### 4 PINNING INFORMATION

#### 4.1 Pinning

# 16-bit microcontroller

P90CE201

# 4.2 Pin description

Table 1 QFP64 package.

| MNEMONIC                                                          | TYPE | PIN NO.                                                                 | FUNCTION                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------|------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXD                                                               | I/O  | 1                                                                       | Receive Data. RXD is the data input for the UART interface.                                                                                                                                                                                                                               |

| SDA2                                                              | I/O  | 2                                                                       | <b>Serial Data 2</b> (open drain). SDA2 is the data signal for the second I <sup>2</sup> C-bus serial interface.                                                                                                                                                                          |

| SCL2                                                              | I/O  | 3                                                                       | <b>Serial Clock 2</b> (open drain). SCL2 is the clock signal for the second I <sup>2</sup> C-bus serial interface.                                                                                                                                                                        |

| GP7/SDA1<br>GP6/SCL1<br>GP0<br>GP1<br>GP2<br>GP3<br>GP4<br>GP5/T1 | I/O  | 4<br>5<br>6<br>7<br>8<br>9<br>10                                        | <b>General Purpose Port</b> (active HIGH, 3-state). The alternative functions are as follows. SCL1 is the clock signal for the first I <sup>2</sup> C-bus serial interface. SDA1 is the data signal for the first I <sup>2</sup> C-bus serial interface. T1 is the input pin for Timer 1. |

| A23/AP7<br>to<br>A16/AP0                                          | I/O  | 12 to 15, 21,<br>22, 24, 23                                             | <b>Address Bus.</b> Upper 8-bits of the address bus (A23 to A16). The unused address bits can be selected as a quasi-bidirectional port (AP).                                                                                                                                             |

| A15 to A0                                                         | 0    | 25, 26, 28, 27,<br>34, 38, 32, 30,<br>29, 31, 33, 35,<br>37, 39, 40, 42 | Address Bus. Lower 16-bits of the address bus.                                                                                                                                                                                                                                            |

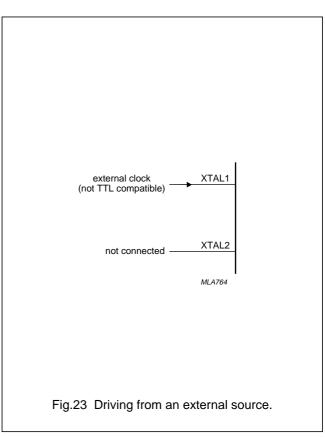

| XTAL2                                                             | 0    | 16                                                                      | Oscillator output. Not connected if an external clock generator is used.                                                                                                                                                                                                                  |

| XTAL1                                                             | I    | 17                                                                      | Oscillator input. XTAL1 can also be used as an external clock input if an external clock generator is used.                                                                                                                                                                               |

| $V_{DD1}$                                                         | -    | 18                                                                      | Supply voltage. For internal logic, address bus, data bus, RWN, CSRAMN, CSROMN, XTAL1 and XTAL2.                                                                                                                                                                                          |

| V <sub>SS1</sub>                                                  | _    | 19                                                                      | <b>Ground.</b> For internal logic, address bus, data bus, RWN, CSRAMN, CSROMN, XTAL1 and XTAL2.                                                                                                                                                                                           |

| R/WN                                                              | 0    | 20                                                                      | <b>Read</b> (active HIGH)/ <b>Write</b> (active LOW). This controls the direction of data flow.                                                                                                                                                                                           |

| CSROMN                                                            | 0    | 36                                                                      | Chip Select ROM (active LOW). This signal selects external ROM.                                                                                                                                                                                                                           |

| D0 to D7                                                          | 0    | 44, 46, 48, 49,<br>47, 45, 43, 41                                       | Data Bus. 8-bit data bus.                                                                                                                                                                                                                                                                 |

| CSRAMN                                                            | 0    | 50                                                                      | Chip Select RAM (active LOW). This signal enables external RAM.                                                                                                                                                                                                                           |

| V <sub>SS2</sub>                                                  | _    | 51                                                                      | Ground. For all other periphery pins (quiet port).                                                                                                                                                                                                                                        |

| $V_{DD2}$                                                         | _    | 52                                                                      | Supply voltage. For all other periphery pins (quiet port).                                                                                                                                                                                                                                |

| RESET                                                             | I    | 53                                                                      | Reset (active HIGH). Input pin for an external reset.                                                                                                                                                                                                                                     |

| ТО                                                                | I    | 54                                                                      | <b>Timer 0.</b> Input pin for cycle and event counting using Timer 0.                                                                                                                                                                                                                     |

| T2                                                                | I    | 55                                                                      | Timer 2. Input pin for cycle and event counting using Timer 2.                                                                                                                                                                                                                            |

# 16-bit microcontroller

P90CE201

| MNEMONIC  | TYPE | PIN NO. | FUNCTION                                                              |

|-----------|------|---------|-----------------------------------------------------------------------|

| LP0/INTN0 | I/O  | 56      | Latched Interrupt inputs (active LOW). A LOW level of ≥ 1 clock pulse |

| LP1/INTN1 |      | 57      | will be stored as a pending interrupt request. Priority levels are    |

| LP2/INTN2 |      | 58      | programmable. Unused interrupt inputs can be used as a                |

| LP3/INTN3 |      | 59      | quasi-bidirectional port (LP).                                        |

| LP4/INTN4 |      | 60      |                                                                       |

| LP5/INTN5 |      | 61      |                                                                       |

| LP6/INTN6 |      | 62      |                                                                       |

| LP7/INTN7 |      | 63      |                                                                       |

| TXD       | 0    | 64      | Transmit Data. TXD is the data output for the UART serial interface.  |

#### 16-bit microcontroller

P90CE201

#### 5 CPU FUNCTIONAL DESCRIPTION

#### 5.1 General

The CPU of the P90CE201 is software compatible with the 68000, consequently programs written for the 68000 will run on the P90CE201 unchanged. However, for certain applications the following differences between the processors should be noted:

- The initialization of the System Control Registers.

- Differences exist in the address error exception processing since the P90CE201 can provide full error recovery.

- The timing is different because of the P90CE201's new architecture and technology. The instruction execution timing is completely different for the same reason.

#### 5.2 Frogramming model and data organization

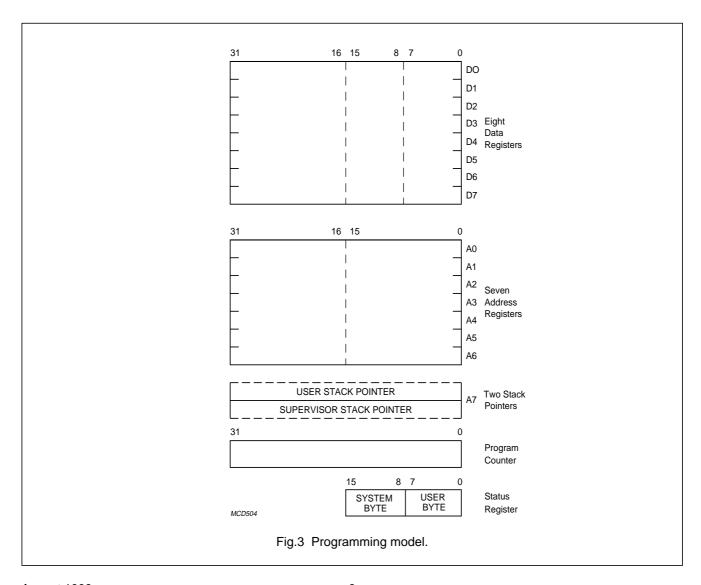

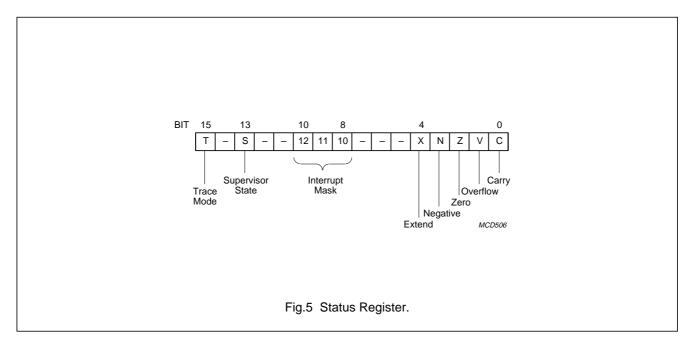

The programming model is identical to that of the 68000 and is shown in Fig.3. It contains seventeen 32-bit registers, a 32-bit Program Counter and a 16-bit Status Register. The first eight registers (D0 to D7) are used as data registers for byte, word and long-word operations. The second group of registers (A0 to A6) and the System Stack Pointer (A7) can be used as software stack pointers and base address registers. In addition, these registers can be used for word and long-word address operations. All seventeen registers can be used as Index Registers.

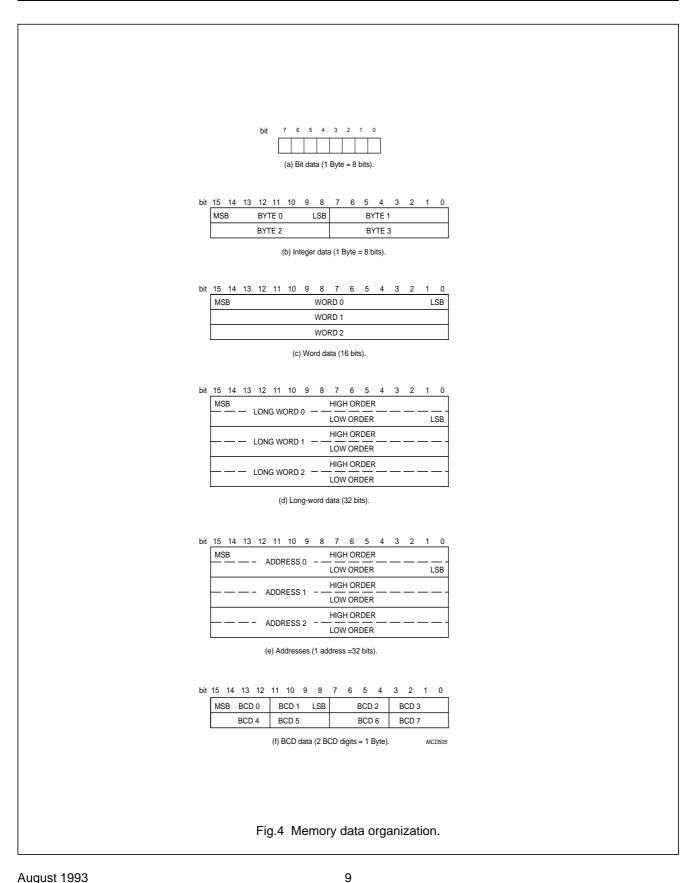

The P90CE201 supports 8, 16 and 32-bit integer data, BCD data 32-bit addresses. Each data type is arranged in memory as shown in Fig.4.

# 16-bit microcontroller

# P90CE201

August 1993

#### 16-bit microcontroller

P90CE201

10

#### 5.3 Internal and external operation

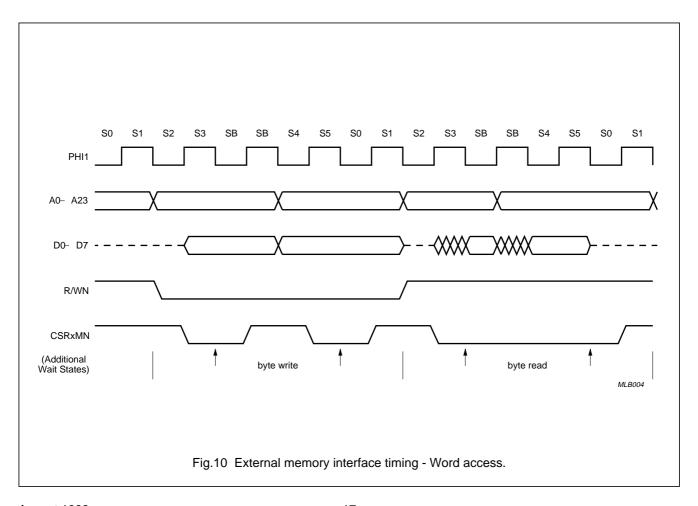

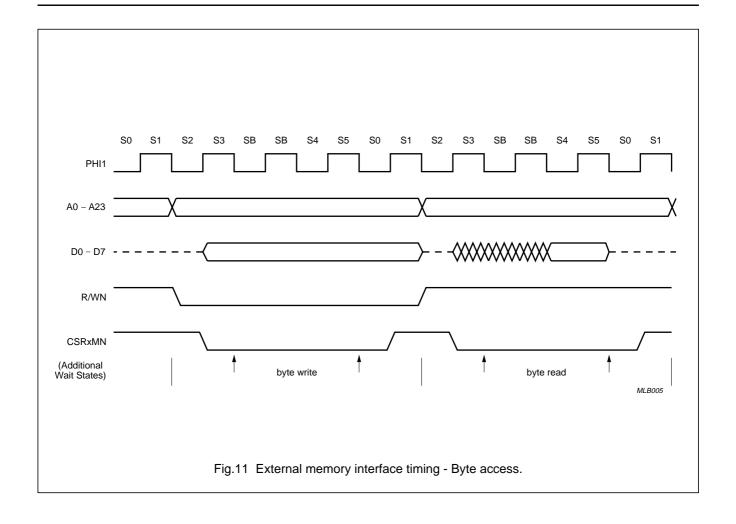

The P90CE201 operates with an internal clock frequency of half the oscillator frequency ( $f_{OSC}/2$ ). Each internal clock cycle is divided into 2 states. A non-access machine cycle has 3 clock cycles or 6 states (S0 to S5). A minimum bus cycle normally consists of 3 clock cycles (6 states). When data transfer has not yet been terminated, wait states (SW) are inserted in multiples of 2. For external memory access, 2 wait states (bus states SB) are added automatically.

#### 5.4 Processing states and exception processing

The CPU is always in one of three processing states: normal, exception or halted.

The normal processing state is that associated with instruction execution; the memory references are to fetch instructions and operands and to store results. A special case of the normal state is the stopped state which the processor enters when a STOP instruction is executed. In this state the CPU makes no further memory references.

The exception processing state is associated with interrupts, trap instructions, tracing and other exceptional conditions. The exception may be generated internally by an instruction or by an unusual condition arising during the execution of an instruction. Externally, exception processing can be forced by an interrupt or a reset.

The halted processing state is an indication of a catastrophic hardware failure. For example, if during exception processing of a bus error another bus error occurs, the CPU assumes that the system is unusable and halts. Only an external reset can restart a halted processor. Note that a CPU in the stopped state is not in the halted state or vice versa.

The processor can work in the "user" or "supervisor" state determined by the state of the S-bit in the Status Register. Accesses to the on-chip peripherals are achieved in the supervisor state.

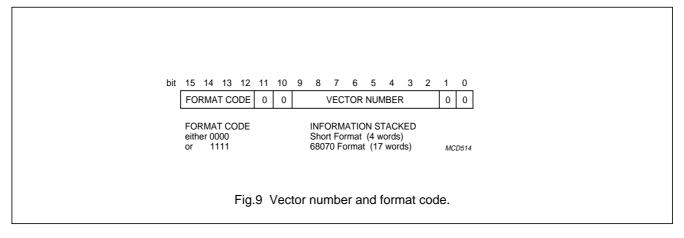

All exception processing is performed in the supervisor state once the current content of the Status Register has been copied. The exception vector number is then determined and copies of the Status Register, the Program Counter value and the format/vector number are saved on the supervisor stack using the Supervisor Stack Pointer. Finally, the contents of the exception vector location is fetched and loaded into the Program Counter.

August 1993

#### 16-bit microcontroller

P90CE201

#### 5.4.1 EXCEPTION VECTORS

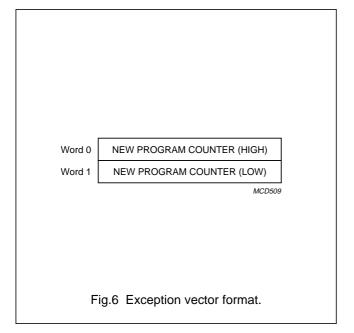

Exception vectors are memory locations from which the CPU fetches the address of a routine that will handle that exception. All exception vectors are 2 words long (see Fig.6) except for the reset vector which is made up of 4 words, containing the Program Counter (PC) and the Supervisor Stack Pointer (SSP). All exception vectors are contained in the supervisor data space.

A vector number is an 8-bit number that, when multiplied by 4, gives the address of an exception vector. Vector numbers are generated internally. The memory map for the exception vectors is given in Table 2.

# 16-bit microcontroller

P90CE201

Table 2 Exception vector assignment.

| VECTOR NO.        | DEC        | HEX       | ASSIGNMENT                           |

|-------------------|------------|-----------|--------------------------------------|

| 0                 | 0          | 000       | Reset: initial SSP                   |

| 1                 | 4          | 004       | Reset: initial PC                    |

| 2                 | 8          | 008       | Bus error                            |

| 3                 | 12         | 00C       | Address error                        |

| 4                 | 16         | 010       | Illegal instruction                  |

| 5                 | 20         | 014       | Zero divide                          |

| 6                 | 24         | 018       | CHK instruction                      |

| 7                 | 28         | 01C       | TRAPV instruction                    |

| 8                 | 32         | 020       | Privilege violation                  |

| 9                 | 36         | 024       | Trace                                |

| 10                | 40         | 028       | Line 1010 emulator                   |

| 11                | 44         | 02C       | Line 1111 emulator                   |

| 12                | 48         | 030       | Unassigned, reserved                 |

| 13 (note 1)       | 52         | 034       | Unassigned, reserved                 |

| 14                | 56         | 038       | Format error                         |

| 15                | 60         | 03C       | Uninitialized interrupt vector       |

| 16 to 23 (note 1) | 64 – 92    | 040 – 05C | Unassigned, reserved                 |

| 24                | 96         | 060       | Spurious interrupt                   |

| 25                | 100        | 064       | Level 1 on-chip interrupt autovector |

| 26                | 104        | 068       | Level 2 on-chip interrupt autovector |

| 27                | 108        | 06C       | Level 3 on-chip interrupt autovector |

| 28                | 112        | 070       | Level 4 on-chip interrupt autovector |

| 29                | 116        | 074       | Level 5 on-chip interrupt autovector |

| 30                | 120        | 078       | Level 6 on-chip interrupt autovector |

| 31                | 124        | 07C       | Level 7 on-chip interrupt autovector |

| 32 to 47          | 128 – 188  | 080 – 0BC | TRAP instruction vectors             |

| 48 to 63 (note 1) | 192 – 252  | 0C0 - 0FC | Unassigned, reserved                 |

| 64 to 255         | 256 – 1020 | 100 – 3FC | User interrupt vectors               |

#### Note

1. Vectors 12, 13, 16 to 23 and 48 to 63 are reserved for future enhancements. No user peripheral devices should be assigned to these numbers.

#### 16-bit microcontroller

P90CE201

#### 5.4.2 MULTIPLE EXCEPTIONS

As two or more exceptions can occur simultaneously, exceptions are grouped in order of priority; as is shown in Table 3.

#### 5.4.3 INSTRUCTION TRAPS

Traps are exceptions caused by instructions arising either from CPU recognition of abnormal conditions during instruction execution or from instructions whose normal behaviour is to cause traps.

Some instructions are used specifically to generate traps. The TRAP instruction always forces an exception, and is useful for implementing system calls for user programs. The TRAPV and CHK instructions force an exception if the user program detects a run-time error, possibly an arithmetic overflow or a subscript out of bounds. The signed divide (DIVS) and unsigned divide (DIVU) instructions will force an exception if a divide-by-zero operation is attempted.

#### 5.4.4 ILLEGAL AND UNIMPLEMENTED INSTRUCTIONS

Illegal instruction is the term used to refer to any word that is not the first word of a legal instruction. During instruction execution, if such an instruction is fetched, an illegal instruction exception occurs. Words with bits 15 to 12 equal to 1010 or 1111 are defined as unimplemented instructions and separate exception vectors are allocated to these patterns for efficient emulation. This facility allows the operating system to detect program errors, or to emulate unimplemented instructions in software.

#### 5.4.5 PRIVILEGE VIOLATIONS

To provide system security, various instructions are privileged and any attempt to execute one of the privileged and any attempt to execute one of the privileged instructions while the CPU is in the user state causes an exception. The privileged instructions are:

- STOP

- RESET

- RTE

- MOVE TO SR

- AND (word) immediate to SR

- . EOR (word) immediate to SR

- · OR (word) immediate to SR

- MOVE USP.

#### 5.4.6 TRACING

The CPU includes a facility to trace instructions one by one to assist in program development. In the trace state, after each instruction is executed, an exception is forced so that a debugging program can monitor execution of the program under test.

The trace facility uses the T-bit in the supervisor part of the Status Register. If the T-bit is cleared, tracing is disabled and instructions execute normally. If the T-bit is set at the beginning of the execution of an instruction, a trace exception will be generated after that instruction is executed. If the instruction is not executed, either because of an interrupt, or because the instruction is illegal or privileged, the trace exception does not occur. Also, the trace exception does not occur if the instruction is aborted by a reset, bus error, or address error exception. If the instruction is executed and an interrupt is pending, the trace exception is processed before the interrupt. If the execution of an instruction forces an exception, the forced exception is processed before the trace exception.

As an extreme illustration of the above rules, consider the arrival of an interrupt during the execution of a TRAP instruction while tracing is enabled. First the trap exception is processed, then the trace exception, and finally the interrupt is processed. Instruction execution resumes in the interrupt handling routine.

Table 3 Exception grouping and priority.

| GROUP | EXCEPTION                                       | PROCESSING                                                            |

|-------|-------------------------------------------------|-----------------------------------------------------------------------|

| 0     | RESET, ADDRESS ERROR<br>BUS ERROR               | Exception processing begins at the next machine cycle.                |

| 1     | TRACE, INTERRUPT,<br>ILLEGAL, PRIVILEGE         | Exception processing begins before the next instruction.              |

| 2     | TRAP, TRAPV, CHK, ZERO,<br>DIVIDE, FORMAT ERROR | Exception processing is started through normal instruction execution. |

#### 16-bit microcontroller

P90CE201

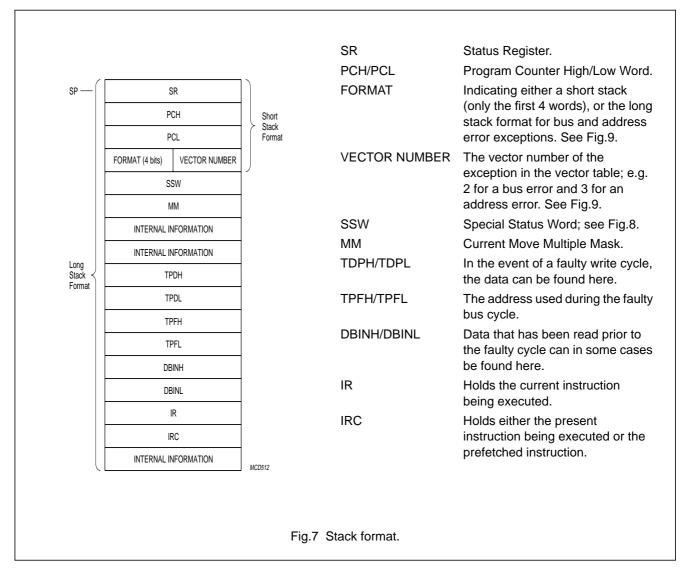

#### 5.5 Stack format

The stack format for exception processing is similar to the 68010 (rather than the 68000) although the information stored is not the same due to the different architecture. To handle this format the P90CE201 differs from the 68000 in that:

- · The stack format has changed.

- The minimum number of words put into, or restored from, the stack is 4 (68010 compatible; not 3 as with the 68000).

- The RTE instruction decides (with the aid of the 4 format bits) whether or not more information has to be restored. The P90CE201 long format is used for bus error and address error exceptions; all other exceptions use the short format.

- If another format code, other than one of the two listed above, is detected during the restore action, a Format Error

occurs.

If the user wants to finish the instruction in which the bus or address error occurred, the P90CE201 format must be used on RTE. If no changes to the stack are required during exception processing, the stack format is transparent to the user.

#### 5.5.1 LONG AND SHORT STACK FORMATS

# 16-bit microcontroller

P90CE201

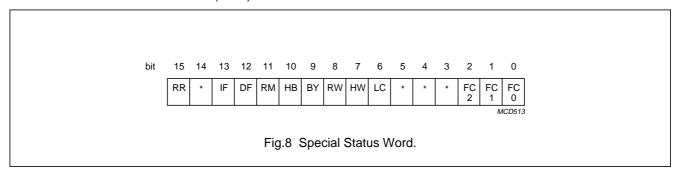

#### 5.5.2 THE SPECIAL STATUS WORD (SSW)

Table 4 Description of SSW.

| SYMBOL | BIT    | FUNCTION                                                                                                                                   |  |

|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| RR     | SSW.15 | Rerun. By default this bit is a logic 0. If set to a logic 1, the CPU will not re-run the faulty bus cycle on return from exception (RTE). |  |

| _      | SSW.14 | Undefined, reserved                                                                                                                        |  |

| IF     | SSW.13 | The faulty cycle was an instruction fetch.                                                                                                 |  |

| DF     | SSW.12 | The faulty cycle was a data fetch.                                                                                                         |  |

| RM     | SSW.11 | The error occurred during a read-modify-write cycle.                                                                                       |  |

| НВ     | SSW.10 | High Byte                                                                                                                                  |  |

| BY     | SSW.9  | The faulty cycle was a byte transfer.                                                                                                      |  |

| RW     | SSW.8  | Read/Write cycle                                                                                                                           |  |

| HW     | SSW.7  | High Word                                                                                                                                  |  |

| LC     | SSW.6  | The faulty cycle was during a long-word access.                                                                                            |  |

| _      | SSW.5  | Undefined, reserved                                                                                                                        |  |

| _      | SSW.4  | Undefined, reserved                                                                                                                        |  |

| _      | SSW.3  | Undefined, reserved                                                                                                                        |  |

| FC2    | SSW.2  | Function Code. These three bits hold the internal function code during the faulty                                                          |  |

| FC1    | SSW.1  | bus cycle. The function codes are the same as for the 68000 and affect the status                                                          |  |

| FC0    | SSW.0  | of the CPU during the faulty bus cycle. See Table 5.                                                                                       |  |

Table 5

Internal function codes.

| FC2 | FC1 | FC0 | ADDRESS SPACE         |

|-----|-----|-----|-----------------------|

| 0   | 0   | 0   | Reserved              |

| 0   | 0   | 1   | User data             |

| 0   | 1   | 0   | User program          |

| 0   | 1   | 1   | Reserved              |

| 1   | 0   | 0   | Reserved              |

| 1   | 0   | 1   | Supervisor data       |

| 1   | 1   | 0   | Supervisor program    |

| 1   | 1   | 1   | Interrupt acknowledge |

#### 16-bit microcontroller

P90CE201

16

#### 5.6 CPU interrupt processing

An Interrupt Controller handles all interrupts, solves any priority problems and passes the highest level interrupt to the CPU. The general interrupt handling mechanism and the Interrupt Controller are described in section 6.2.

The CPU interrupt handling follows the same basic rules as in the 68000. However, the following changes have been made to simplify system development:

- Interrupts with a priority level equal to or less than the priority level actually running will not be accepted.

- During the acknowledge cycle of an interrupt, the IPL bits of the Status Register are set to the priority level of the acknowledged interrupt. An exception to this is when the IM bit in SYSCON2 is a logic 0. In this case level 7 is loaded into the Status Register. See section 6.1.2.

If the priority of the interrupt pending is greater than the current processor priority then:

- The exception processing sequence is started.

- · A copy of the Status Register is saved.

- The privilege level is set to supervisor state.

- Tracing is suppressed.

- The priority level of the processor is set to that of the interrupt being acknowledged.

The processor then gets the vector number from the interrupting device, classifies it as an interrupt acknowledge, and displays the interrupt level number being acknowledged on the address bus.

If autovectoring is requested by the interrupting device, the processor internally generates a vector number that corresponds to the interrupt level number.

The processor then starts normal exception processing by saving the format word, Program Counter, and Status Register in the supervisor stack. The value of the vector in the format word is either supplied externally by the requesting device or is an internally generated vector number multiplied by four (format is all zeros). The Program Counter value is the address of the instruction that would have been executed if the interrupt had not been present. Then the interrupt vector contents are fetched and loaded into the Program Counter. The interrupt handling routine starts with normal instruction execution.

Priority level 7 is a special case; it can only be detected if the priority level was set to a lower value in between.

August 1993

#### 16-bit microcontroller

P90CE201

#### 6 SYSTEM CONTROL

#### 6.1 Memory mapping

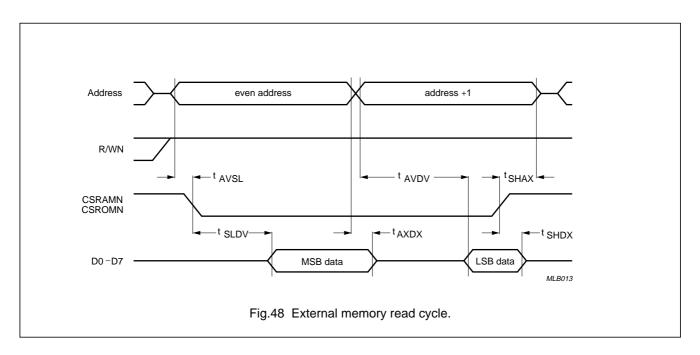

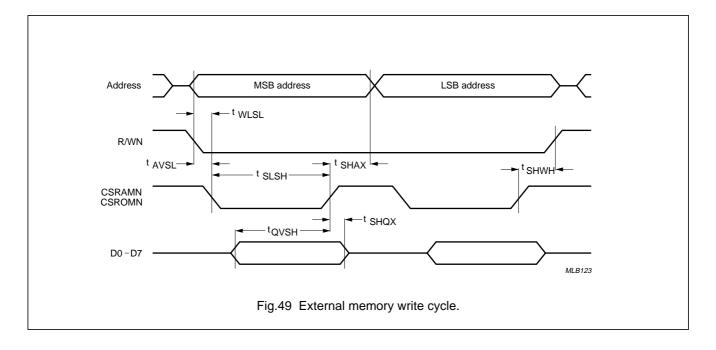

The P90CE201 accesses the external ROM and RAM via 8 data lines and up to 24 address lines. Data access to or from the memories is bytewise. The data will be split or restructured internally to match the internal 16-bit data format. The upper byte (bits 15 to 8) of the data is taken from the even address, the lower byte (bits 7 to 0) from the odd address (MSB address  $\pm$  1).

For external memory control the device provides the R/WN signal together with chip enable signals for ROM (CSROMN) and RAM (CSRAMN). CSROMN is activated in the internal address range 0H to FFFFFH. The CSRAMN signal is activated in the internal address range 1000000H to 1FFFFFFH. In the external world RAM and ROM are wired in parallel with a maximum address range of 16 Mbytes each. If the larger memory of RAM or ROM is smaller than 16 Mbytes the unused address pins can be used as port pins. The advantages of this addressing scheme are:

- · Maximum flexibility for RAM and ROM sizes.

- The full physical memory size can be used without any restrictions.

- The minimum number of address pins are used.

The validity of data is signalled to the CPU by the internal signal DTACKN. This signal is generated internally after a programmable delay (wait states). By programming the number of wait cycles the user can adapt the program execution times to his memory access times. After reset the delay for the DTACKN signal is set to its maximum value. Programming the number of wait cycles is described in section 6.3.2.

# 16-bit microcontroller

P90CE201

#### 16-bit microcontroller

P90CE201

#### 6.2 Interrupt controller

An interrupt controller handles all internal and external interrupts. It passes the interrupt with the highest level priority to the CPU.

The following interrupt requests are generated by the on-chip peripherals.

- I<sup>2</sup>C1

- I<sup>2</sup>C2

- UART receiver

- UART transmitter

- Timer 2

- Timer 1

- Timer 0.

The following interrupt requests are sent via external pins.

INTN0 to INTN7

#### 6.2.1 INTERRUPT ARBITRATION

The priority level of all interrupts are programmable and each may be allocated a value between 0 and 7. Level 7 has the highest priority, level 0 disables the corresponding interrupt source. In the event of interrupt requests of equal priority level occurring at the same time, then a hardware mechanism gives the following order.

- INTN7

- INTN6

- INTN5

- INTN4

- INTN3

- INTN2

- INTN1

- INTN0

- Timer 2

- Timer 1

- Timer 0

- UART receiverUART transmitter

- I<sup>2</sup>C2

- I<sup>2</sup>C1.

The execution of interrupt routines may be interrupted by another higher priority level interrupt request (nested interrupts). In the 68070 mode (SYSCON2.7 = 1), when an interrupt is serviced by the CPU, the corresponding level is loaded into the Status Register. This prevents the current interrupt from getting interrupted by another interrupt request with the same or lower priority level. If SYSCON2.7 = 0, priority level 7 will always be loaded into the Status Register and therefore the current interrupt cannot be interrupted by any other interrupt request.

#### 6.2.2 ACKNOWLEDGE AND INTERRUPT VECTORS

When the CPU is ready to service a particular interrupt request, it initiates an "interrupt acknowledge cycle" in order to obtain the interrupt vector from the requesting device. When the device recognizes that its interrupt request has been accepted it either provides an 8-bit interrupt vector together with an internal DTACKN signal (vector mode), or it asserts an internal AVN signal and the interrupt vector is calculated from the interrupt level.

#### 6.2.3 EXTERNAL LATCHED INTERRUPTS

INTN7 to INTN0 are 8 external interrupt inputs; each triggered on the falling edge of the input. Their priority levels as well as their interrupt vectors are programmable.

As an alternative function INTN7 to INTN0 may be used as I/O ports. When an interrupt pin is programmed as a port, the corresponding bit in the Port Control Register LPCRH (or LPCRL) is used for port I/O. A read from either of these two registers reads the value from the corresponding bit in the Port Control Register. A read from the Port Pad Control Register LPPH (or LPPL) reads the value from the corresponding port input pin. A write to LPCRH (or LPCRL) or to LPPH (or LPPL) writes the value to the corresponding port register, from where it is driven to the corresponding port pin.

The port function is configured as a quasi-bidirectional port. A bit is set to input mode by writing a logic 1 to the corresponding Port Control Register bit. This drives a "weak" logic 1 to the corresponding output pin, which can be overwritten by an external signal.

In the following register descriptions "n" represents the external interrupt number (0 to 7), its associated registers are identified using the same number.

# 16-bit microcontroller

P90CE201

#### 6.2.4 LATCHED INTERRUPT REGISTER n (LIRn)

| bit 7  | bit 6  | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|--------|--------|-------|-------|-------|-------|-------|-------|

| INTNC1 | INTNC0 | AVN   | -     | PIR   | IPL2  | IPL1  | IPL0  |

Fig.12 Latched Interrupt Register n (LIRn).

#### Table 6 Description of LIRn bits.

| SYMBOL               | BIT                        | FUNCTION                                                                                                                                                                                                                                                                                                                                         |

|----------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTNC1<br>INTNC0     | LIRn.7<br>LIRn.6           | Interrupt Control. These two bits enable/disable the external interrupt INTNn, or select the pin as an I/O port. See Table 7.                                                                                                                                                                                                                    |

| AVN                  | LIRn.5                     | Autovector. When AVN = 0; INTNn is an autovectored interrupt and the processor calculates the appropriate vector from a fixed vector table. This is also the default value. When AVN = 1; INTNn is a vectored interrupt and the peripheral must provide an 8-bit vector number.                                                                  |

| _                    | LIRn.4                     | Not used; reserved                                                                                                                                                                                                                                                                                                                               |

| PIR                  | LIRn.3                     | Pending Interrupt Request. If PIR = 1; then a valid interrupt request has been detected. It is automatically reset by the interrupt acknowledge cycle from the CPU. If PIR = 0; there is no pending interrupt request; this is also the default value. PIR can be set or reset by software by writing a logic 1 or logic 0 respectively to PIRn. |

| IPL2<br>IPL1<br>IPL0 | LIRn.2<br>LIRn.1<br>LIRn.0 | Interrupt Priority Level. These three bits select the interrupt priority level for the external interrupt INTNn. See Table 8.                                                                                                                                                                                                                    |

#### Table 7 Interrupt INTNn control.

| INTNC1 | INTNC0 | INTERRUPT CONTROL                                   |  |  |

|--------|--------|-----------------------------------------------------|--|--|

| 0      | 0      | Interrupt disabled; this is also the default value. |  |  |

| 0      | 1      | interrupt enabled                                   |  |  |

| 1      | 0      | Interrupt pin is selected as an I/O port.           |  |  |

| 1      | 1      | Reserved                                            |  |  |

#### Table 8 Selection of interrupt priority level.

| IPL2 | IPL1 | IPL0 | PRIORITY LEVEL                                       |

|------|------|------|------------------------------------------------------|

| 0    | 0    | 0    | Interrupt inhibited; this is also the default value. |

| 0    | 0    | 1    | Level 1                                              |

| 0    | 1    | 0    | Level 2                                              |

| 0    | 1    | 1    | Level 3                                              |

| 1    | 0    | 0    | Level 4                                              |

| 1    | 0    | 1    | Level 5                                              |

| 1    | 1    | 0    | Level 6                                              |

| 1    | 1    | 1    | Level 7                                              |

# 16-bit microcontroller

P90CE201

#### 6.2.5 LATCHED INTERRUPT VECTOR n (LIVn)

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IV.7  | IV.6  | IV.5  | IV.4  | IV.3  | IV.2  | IV.1  | IV.0  |

Fig.13 Latched Interrupt Vector n (LIVn).

#### Table 9 Description of LIVn bits.

| SYMBOL       | BIT              | FUNCTION                                                                  |

|--------------|------------------|---------------------------------------------------------------------------|

| IV.7 to IV.0 | LIVn.7 to LIVn.0 | 8-bit interrupt vector number. The default value of this register is 0FH. |

#### 6.2.6 LATCHED PORT CONTROL REGISTER HIGH (LPCRH)

| b  | oit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|----|-------|-------|-------|-------|-------|-------|-------|-------|

| IN | ITN7  | _     | INTN6 | _     | INTN5 | _     | INTN4 | -     |

Fig.14 Latched Port Control Register High (LPCRH).

#### 6.2.7 LATCHED PORT CONTROL REGISTER LOW (LPCRL)

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| INTN3 | _     | INTN2 | _     | INTN1 | _     | INTN0 | _     |

Fig.15 Latched Port Control Register Low (LPCRL).

# 16-bit microcontroller

P90CE201

#### 6.2.8 LATCHED PORT PIN REGISTER HIGH (LPPH)

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| INTN7 | _     | INTN6 | 1     | INTN5 | -     | INTN4 | _     |

Fig.16 Latched Port Pin Register High (LPPH).

# 6.2.9 LATCHED PORT PIN REGISTER LOW (LPPL)

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| INTN3 | _     | INTN2 | _     | INTN1 | _     | INTN0 | _     |

Fig.17 Latched Port Pin Register Low (LPPL).

#### 16-bit microcontroller

P90CE201

#### 6.3 System Control Registers

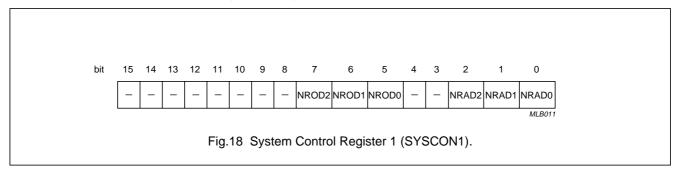

The P90CE201 has two System Control Registers SYSCON1 and SYSCON2 which allow system parameters to be selected.

#### 6.3.1 SYSTEM CONTROL REGISTER 1 (SYSCON1)

Table 10 Description of SYSCON1 bits.

| SYMBOL | BIT        | FUNCTION                                                                          |

|--------|------------|-----------------------------------------------------------------------------------|

| _      | SYSCON1.15 | These eight bits are not used.                                                    |

|        | to         |                                                                                   |

|        | SYSCON1.8  |                                                                                   |

| NROD2  | SYSCON1.7  | These three bits select the access time for the ROM area. After a reset operation |

| NROD1  | SYSCON1.6  | these bits are logic 0's. See Table 11.                                           |

| NROD0  | SYSCON1.5  |                                                                                   |

| _      | SYSCON1.4  | not used                                                                          |

| _      | SYSCON1.3  | not used                                                                          |

| NRAD2  | SYSCON1.2  | These three bits select the access time for the RAM area. After a reset operation |

| NRAD1  | SYSCON1.1  | these bits are logic 0's. See Table 11                                            |

| NRAD0  | SYSCON1.0  |                                                                                   |

Table 11 Selection of memory access times for ROM and RAM areas.

| NROD2 | NROD1 | NROD0 | ADD WAIT |     |     | UNIT |     |      |

|-------|-------|-------|----------|-----|-----|------|-----|------|

| NRAD2 | NRAD1 | NRAD0 | STATES   | 24  | 20  | 16   | 12  | UNII |

| 0     | 0     | 0     | 8        | 185 | 235 | 310  | 435 | ns   |

| 0     | 0     | 1     | 4        | 101 | 135 | 185  | 268 | ns   |

| 0     | 1     | 0     | 2        | 60  | 85  | 122  | 185 | ns   |

| 0     | 1     | 1     | 0        | 18  | 35  | 60   | 101 | ns   |

#### **Notes**

- 1. 1 internal clock cycle contains 2 wait states.

- 2. All other states are undefined and reserved.

# 16-bit microcontroller

P90CE201

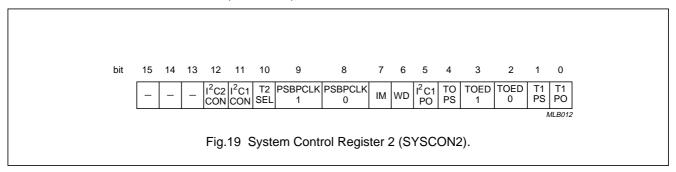

#### 6.3.2 SYSTEM CONTROL REGISTER 2 (SYSCON2)

Table 12 Description of SYSCON2 bits.

| SYMBOL               | BIT                            | FUNCTION                                                                                                                                                                                                                                                                                                                      |

|----------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -                    | SYSCON2.15<br>to<br>SYSCON2.13 | These three bits are not used.                                                                                                                                                                                                                                                                                                |

| I <sup>2</sup> C2CON | SYSCON2.12                     | This bit along with the three bits CR0, CR1 and CR2 held in the Serial Control Register (S2CON), are used to select the bitrate of the $I^2$ C-bus 2 interface. If $I^2$ C2CON = 0; the interface operates with a high bitrate. If $I^2$ C2CON = 1; the interface operates with a low bitrate.                                |

| I <sup>2</sup> C1CON | SYSCON2.11                     | This bit along with the three bits CR0, CR1 and CR2 held in the Serial Control Register (S1CON), are used to select the bitrate of the $I^2$ C-bus 1 interface. If $I^2$ C1CON = 0; the interface operates with a high bitrate. If $I^2$ C1CON = 1; the interface operates with a low bitrate.                                |

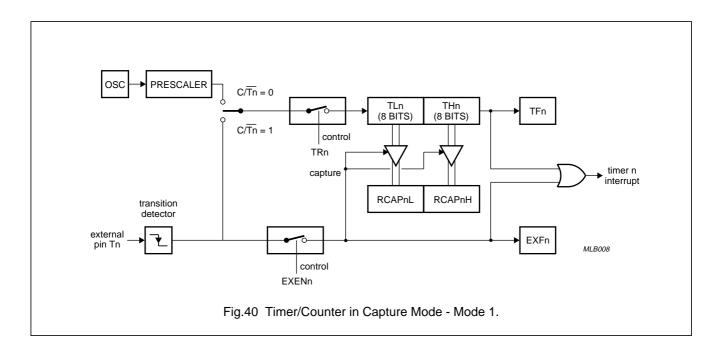

| T2SEL                | SYSCON2.10                     | This bit selects the frequency of the clock for Timer 2. If T2SEL = 0; the timer operates at a frequency of $f_{XTAL}/2$ . If T2SEL = 1; the timer operates at a frequency of BPCLK/4.                                                                                                                                        |

| PSBPCLK1<br>PSBPCLK0 | SYSCON2.9<br>SYSCON2.8         | These two bits control the prescaler for the basic peripheral clock. See Table 13.                                                                                                                                                                                                                                            |

| IM                   | SYSCON2.7                      | If IM = 0; level 7 is loaded into the Status Register during interrupt processing to prevent the CPU from being interrupted by another interrupt source. If IM = 1; the current interrupt level is loaded into the Status Register allowing nested interrupts.                                                                |

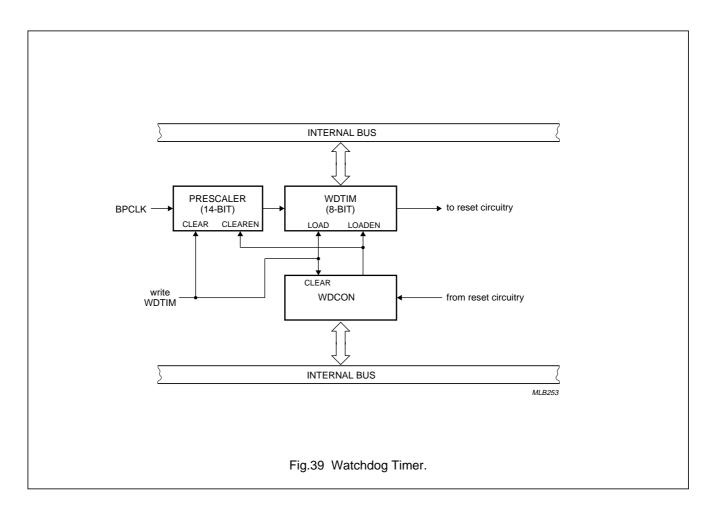

| WD                   | SYSCON2.6                      | This bit enables or disables the Watchdog timer for bus error (internal) detection. If WD = 0; the timer is disabled. If WD = 1; the timer is enabled for bus error detection. If no acknowledge has been sent by the addressed device after $128 \times 16$ internal clock cycles the on-chip bus error signal is activated. |

| I <sup>2</sup> C1PO  | SYSCON2.5                      | The state of this bit determines whether general port pins GP.7/SDA1 and GP.6/SCL1 are used as port pins or in their $I^2$ C-bus function. When $I^2$ C1P0 = 0; the port function is selected. When $I^2$ C1P0 = 1; the $I^2$ C-bus is selected.                                                                              |

| TOPS                 | SYSCON2.4                      | This bit enables or disables the prescaler for Timer 0. If T0PS = 0; the prescaler is disabled and the timer operates at a frequency of $f_{XTAL}/2$ . If T0PS = 1; the prescaler is enabled and the timer operates at a frequency of $f_{XTAL}/32$ .                                                                         |

| T0ED1<br>T0ED0       | SYSCON2.3<br>SYSCON2.2         | These two bits select which transition at the external input will trigger an increment of Timer 0. See Table 14.                                                                                                                                                                                                              |

# 16-bit microcontroller

P90CE201

| SYMBOL | BIT       | FUNCTION                                                                                                                                                                                                                                              |  |

|--------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| T1PS   | SYSCON2.1 | This bit enables or disables the prescaler for Timer 1. If T1PS = 0; the prescaler is disabled and the timer operates at a frequency of $f_{XTAL}/2$ . If T1PS = 1; the prescaler is enabled and the timer operates at a frequency of $f_{XTAL}/32$ . |  |

| T1PO   | SYSCON2.0 | This bit selects whether bit 5 of the general purpose port acts as a port or as an input to Timer 1. If T1PO = 0; bit 5 of the general purpose port acts as a port. If T1PO = 1; bit 5 of the general purpose port acts as an input to Timer 1.       |  |

#### Note

1. All bits of this register have a default value of logic 0 except TOED1 which has a default value of logic 1.

**Table 13** Selection of basic peripheral clock for BPCLK = 4 MHz.

| PSBPCLK1 | PSBPCLK0 | DIVISOR | f <sub>XTAL</sub> (MHz) |

|----------|----------|---------|-------------------------|

| 0        | 0        | 3.0     | 24                      |

| 0        | 1        | 2.5     | 20                      |

| 1        | 0        | 2.0     | 16                      |

| 1        | 1        | 1.5     | 12                      |

Table 14 Selection of input trigger for T0.

| TOED1 | TOED0 | TRANSITION                                                                                    |  |

|-------|-------|-----------------------------------------------------------------------------------------------|--|

| 0     | 0     | Edge detection disabled                                                                       |  |

| 0     | 1     | LOW-to-HIGH transitions will be monitored.                                                    |  |

| 1     | 0     | HIGH-to-LOW transitions will be monitored. This is the default value after a reset operation. |  |

| 1     | 1     | Any transition will be monitored.                                                             |  |

#### 16-bit microcontroller

P90CE201

#### 6.4 Reset

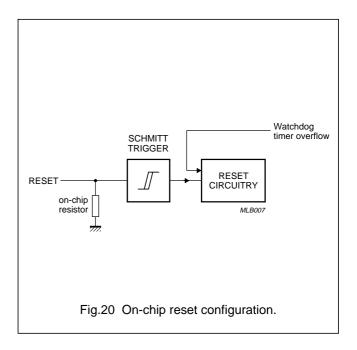

The reset input for the P90CE201 is RESET (pin 53). A Schmitt trigger is used at the input for noise rejection. The output of the Schmitt trigger is sampled by the reset circuitry every machine cycle. The internal reset circuitry has an additional input which is activated by an overflow of the Watchdog Timer (WDTIM). The On-chip Reset configuration is shown in Fig.20.

A global reset may be performed by three different methods:

- Applying an external signal to the RESET pin

- · Automatic Power-on-reset circuitry

- Activated by an overflow of the Watchdog Timer.

During the reset operation the CPU and peripherals are reset. After an internal start-up time, the CPU reads the reset vectors (the reset vectors are four words long). Address 000000H is loaded into the Supervisor Stack Pointer (SSP), and address 000004H is loaded into the Program Counter (PC). As soon as the SSP and PC have been loaded, the CPU initializes the Status Register to interrupt level 7. Instruction execution then starts at the address indicated by the Program Counter.

#### 6.4.1 EXTERNAL RESET USING THE RESET PIN

An external reset is accomplished by applying an external signal to the RESET pin. To ensure that the oscillator is stable before the controller starts, the external signal must be held HIGH for at least 100 ms.

#### 6.4.2 AUTOMATIC POWER-ON RESET

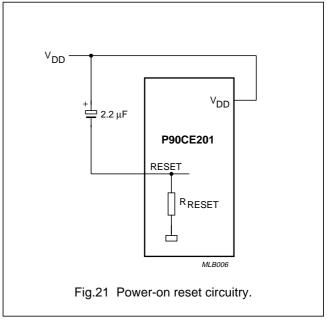

Providing the rise time of  $V_{DD}$  does not exceed 10 ms, an automatic reset can be obtained by connecting the RESET pin to  $V_{DD}$ , via a 2.2  $\mu$ F capacitor. When the power is switched on, the voltage on the RESET pin is equal to  $V_{DD}$  minus the capacitor voltage, and decreases from  $V_{DD}$  as the capacitor charges through the internal resistor ( $R_{RESET}$ ) to ground. The larger the capacitor, the more slowly  $V_{RESET}$  decreases.  $V_{RESET}$  must remain above the lower threshold of the Schmitt trigger long enough to effect a complete reset. The time required is the oscillator start-up time, plus 2 machine cycles. The Power-on reset circuitry is shown in Fig.21.

# 6.4.3 RESET ACTIVATED BY AN OVERFLOW OF THE WATCHDOG TIMER

A reset can also be initiated by an overflow of the Watchdog Timer (see Fig.20). After a reset operation the Watchdog Timer is disabled.

Note that when the CPU executes a RESET instruction, the CPU is not affected, only the on-chip peripherals are reset.

## 16-bit microcontroller

P90CE201

#### 6.5 Clock circuitry

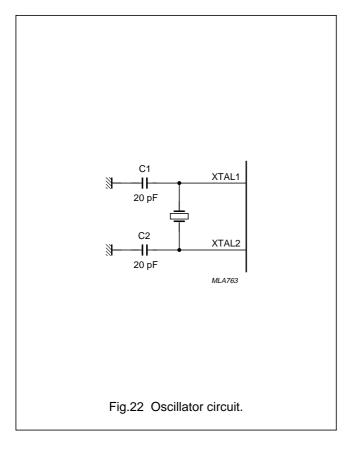

The oscillator circuit of the P90CE201 is a single-stage inverting amplifier in a Pierce oscillator configuration. The circuitry between XTAL1 and XTAL2 is basically an inverter biased to the transfer point. Either a crystal or ceramic resonator can be used as the feedback element to complete the oscillator circuitry. Both are operated in parallel resonance. XTAL1 is the high gain amplifier input, and XTAL2 is the input; see Fig.22. To drive the P90CE201 externally, XTAL1 is driven from an external source and XTAL2 left open-circuit; see Fig.23.

The P90CE201 is specified for a maximum crystal frequency of 24 MHz. The internal clock frequency is the crystal frequency ( $f_{XTAL}$ ) divided by 2. For some peripherals such as the UART and Watchdog Timer, a main prescaler generates a basic peripheral clock. Frequencies other than the basic peripheral clock will be generated within the peripherals. The prescaler is programmed by register SYSCON2. Table 15 shows the frequencies of the basic peripheral clock generated by the main prescaler.

**Table 15** Basic peripheral clock frequencies.

| £ (RALI=)               | £ (8411-)              | f <sub>INT</sub> DIVISOR (MHz) |      |      |      |  |  |  |  |  |

|-------------------------|------------------------|--------------------------------|------|------|------|--|--|--|--|--|

| f <sub>XTAL</sub> (MHz) | f <sub>INT</sub> (MHz) | 3                              | 2.5  | 2    | 1.5  |  |  |  |  |  |

| 24                      | 12                     | 4.00                           | 4.80 | 6.00 | 8.00 |  |  |  |  |  |

| 20                      | 10                     | 3.33                           | 4.00 | 5.00 | 6.66 |  |  |  |  |  |

| 16                      | 8                      | 2.66                           | 3.20 | 4.00 | 5.33 |  |  |  |  |  |

| 12                      | 6                      | 2.00                           | 2.40 | 3.00 | 4.00 |  |  |  |  |  |

# 16-bit microcontroller

P90CE201

#### 7 INSTRUCTION SET

The P90CE201 is completely code compatible with the 68000. Consequently, programs developed for the 68000 will run on the P90CE201. This applies to both the source and object codes. The instruction set was designed to minimize the number of mnemonics that the programmer has to remember.

| MNEMONIC         | DESCRIPTION                        | OPERATION                                                                                                   | CONDITION CODES |   |   |   |   |  |  |  |

|------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------|---|---|---|---|--|--|--|

| ININEMONIC       | DESCRIPTION                        | OPERATION                                                                                                   | Х               | N | Z | ٧ | С |  |  |  |

| ABCD             | Add Decimal with Extend            | $(Destination)_{10} + (Source)_{10} + X \rightarrow Destination$                                            | *               | U | * | U | * |  |  |  |

| ADD              | Add Binary                         | (Destination) + (Source) → Destination                                                                      | *               | * | * | * | * |  |  |  |

| ADDA             | Add Address                        | (Destination) + (Source) $\rightarrow$ Destination                                                          | _               | _ | _ | _ | - |  |  |  |

| ADDI             | Add Immediate                      | (Destination) + Immediate Data $\rightarrow$ Destination                                                    | *               | * | * | * | * |  |  |  |

| ADDQ             | Add Quick                          | (Destination) + Immediate Data $\rightarrow$ Destination                                                    | *               | * | * | * | * |  |  |  |

| ADDX             | Add Extended                       | (Destination) + (Source) + $X \rightarrow$ Destination                                                      | *               | * | * | * | * |  |  |  |

| AND              | AND Logical                        | (Destination) $\Lambda$ (Source) $\rightarrow$ Destination                                                  | _               | * | * | 0 | 0 |  |  |  |

| ANDI             | AND Immediate                      | (Destination) $\Lambda$ Immediate Data $\rightarrow$ Destination                                            | _               | * | * | 0 | 0 |  |  |  |

| ASL, ASR         | Arithmetic Shift                   | (Destination) Shifted by $<$ count $> \rightarrow$ Destination                                              | *               | * | * | * | * |  |  |  |

| B <sub>CC</sub>  | Branch Conditionally               | If CC then PC + d $\rightarrow$ PC                                                                          | _               | - | _ | _ | - |  |  |  |

| BCHG             | Test a Bit and Change              | ~(< bit number >) of Destination → Z<br>~(< bit number >) of Destination →<br>< bit number > of Destination | _               | - | * | - | - |  |  |  |

| BCLR             | Test a Bit and Clear               | ~(< bit number >) of Destination $\rightarrow$ Z                                                            | _               | - | * | - | - |  |  |  |

| BRA              | Branch Always                      | $PC + d \rightarrow PC$                                                                                     | _               | - | - | - | - |  |  |  |

| BSET             | Test a Bit and Set                 | ~(< bit number >) of Destination → Z<br>1 → < bit number > of Destination                                   | _               | - | * | _ | _ |  |  |  |

| BSR              | Branch to Subroutine               | $PC \rightarrow SP @ -; PC + d \rightarrow PC$                                                              | _               | _ | _ | _ | - |  |  |  |

| BTST             | Test a Bit                         | ~(< bit number >) of Destination $\rightarrow$ Z                                                            | _               | _ | * | _ | - |  |  |  |

| СНК              | Check Register against Bounds      | If Dn < 0 or Dn > (< source >) then TRAP                                                                    | _               | * | U | U | U |  |  |  |

| CLR              | Clear an Operand                   | $0 \rightarrow \text{Destination}$                                                                          | _               | 0 | 1 | 0 | 0 |  |  |  |

| CMP              | Compare                            | (Destination) – (Source)                                                                                    | _               | * | * | * | * |  |  |  |

| CMPA             | Compare Address                    | (Destination) – (Source)                                                                                    | _               | * | * | * | * |  |  |  |

| CMPI             | Compare Immediate                  | (Destination) – Immediate Data                                                                              | _               | * | * | * | * |  |  |  |

| СМРМ             | Compare Memory                     | (Destination) – (Source)                                                                                    | _               | * | * | * | * |  |  |  |

| DB <sub>CC</sub> | Test Condition, Decrement & Branch | If (not CC) then $Dn - 1 \rightarrow Dn$ ; if $Dn \neq -1$ then PC $+d \rightarrow PC$                      | _               | - | - | - | _ |  |  |  |

| DIVS             | Signed Divide                      | (Destination) / (Source) $\rightarrow$ Destination                                                          | _               | * | * | * | 0 |  |  |  |

| DIVU             | Unsigned Divide                    | (Destination) / (Source) $\rightarrow$ Destination                                                          | _               | * | * | * | 0 |  |  |  |

# 16-bit microcontroller

P90CE201

|                 | DESCRIPTION                          | 00-04-04                                                          | CONDITION CODES |   |   |   |   |  |  |  |

|-----------------|--------------------------------------|-------------------------------------------------------------------|-----------------|---|---|---|---|--|--|--|

| MNEMONIC        | DESCRIPTION                          | OPERATION                                                         | Х               | N | Z | ٧ | С |  |  |  |

| EOR             | Exclusive OR Logical                 | (Destination) ⊕ (Source) → Destination                            | _               | * | * | 0 | 0 |  |  |  |

| EORI            | Exclusive OR Immediate               | (Destination) ⊕ Immediate Data → Destination                      | _               | * | * | 0 | 0 |  |  |  |

| EXG             | Exchange Register                    | $Rx \leftrightarrow Ry$                                           | _               | _ | _ | _ | _ |  |  |  |

| EXT             | Sign Extend                          | (Destination) Sign – extended → Destination                       | _               | * | * | 0 | 0 |  |  |  |

| JMP             | Jump                                 | Destination → PC                                                  | _               | _ | _ | _ | _ |  |  |  |

| JSR             | Jump to Subroutine                   | $PC \rightarrow SP @ -$ ; Destination $\rightarrow PC$            | _               | _ | _ | _ | _ |  |  |  |

| LEA             | Load Effective Address               | Destination → An                                                  | _               | _ | _ | _ | _ |  |  |  |

| LINK            | Link and Allocate                    | $An \rightarrow SP @ -; SP \rightarrow An; SP + d \rightarrow SP$ | _               | _ | _ | _ | _ |  |  |  |

| LSL, LSR        | Logical Shift                        | (Destination) Shifted by < count > → Destination                  | *               | * | * | 0 | * |  |  |  |

| MOVE            | Move Data from Source to Destination | (Source) → Destination                                            | -               | * | * | 0 | 0 |  |  |  |

| MOVE to<br>CCR  | Move to Condition Code               | $(Source) \rightarrow CCR$                                        | *               | * | * | * | * |  |  |  |

| MOVE to<br>SR   | Move to the Status<br>Register       | $(Source) \rightarrow SR$                                         | *               | * | * | * | * |  |  |  |

| MOVE from<br>SR | Move from the Status<br>Register     | SR 	o Destination                                                 | -               | - | - | _ | - |  |  |  |

| MOVE USP        | Move User Stack Pointer              | $USP \rightarrow An; An \rightarrow USP$                          | _               | _ | _ | _ | _ |  |  |  |

| MOVEA           | Move Address                         | (Source) → Destination                                            | _               | _ | _ | _ | _ |  |  |  |

| MOVEM           | Move Multiple Registers              | Registers → Destination; (Source) → Registers                     | _               | _ | _ | _ | _ |  |  |  |

| MOVEP           | Move Peripheral Data                 | (Source) → Destination                                            | _               | _ | _ | _ | _ |  |  |  |

| MOVEQ           | Move Quick                           | Immediate Data → Destination                                      | _               | * | * | 0 | 0 |  |  |  |

| MULS            | Signed Multiply                      | (Destination) * (Source) → Destination                            | -               | * | * | * | 0 |  |  |  |

| MULU            | Unsigned Multiply                    | (Destination) * (Source) → Destination                            | _               | * | * | * | 0 |  |  |  |

| NBCD            | Negate Decimal with Extend           | $0 - (Destination)_{10} - X \rightarrow Destination$              | *               | U | * | U | * |  |  |  |

| NEG             | Negate                               | $0 - (Destination) \rightarrow Destination$                       | *               | * | * | * | * |  |  |  |

| NEGX            | Negate with Extend                   | $0 - (Destination) - X \rightarrow Destination$                   | *               | * | * | * | * |  |  |  |

| NOP             | No Operation                         | _                                                                 | -               | _ | _ | _ | _ |  |  |  |

# 16-bit microcontroller

P90CE201

|                 |                                       |                                                                             | CONDITION CODES |   |   |   |   |  |  |  |

|-----------------|---------------------------------------|-----------------------------------------------------------------------------|-----------------|---|---|---|---|--|--|--|

| MNEMONIC        | DESCRIPTION                           | OPERATION                                                                   | Х               | N | Z | ٧ | С |  |  |  |

| NOT             | Logical Complement                    | ~(Destination) → Destination                                                | _               | * | * | 0 | 0 |  |  |  |

| OR              | Inclusive OR Logical                  | (Destination) v (Source) → Destination                                      | _               | * | * | 0 | 0 |  |  |  |

| ORI             | Inclusive OR Immediate                | (Destination) v Immediate Data → Destination                                | _               | * | * | 0 | 0 |  |  |  |

| PEA             | Push Effective Address                | Destination → SP @-                                                         | _               | _ | _ | _ | _ |  |  |  |

| RESET           | Reset External Devices                | _                                                                           | _               | _ | _ | _ | _ |  |  |  |

| ROL, ROR        | Rotate (Without Extend)               | (Destination) Rotated by < count > → Destination                            | _               | * | * | 0 | * |  |  |  |

| ROXL,<br>ROXR   | Rotate with Extend                    | (Destination) Rotated by < count > → Destination                            | *               | * | * | 0 | * |  |  |  |

| RTE             | Return from Exception                 | $SP @ + \rightarrow SR; SP @ + \rightarrow PC$                              | *               | * | * | * | * |  |  |  |

| RTR             | Return and Restore<br>Condition Codes | $SP \ @ + \to SR;  SP \ @ + \to PC$                                         | *               | * | * | * | * |  |  |  |

| RTS             | Return from Subroutine                | SP @ + → PC                                                                 | _               | _ | _ | _ | _ |  |  |  |

| SBCD            | Subtract Decimal with Extend          | $(Destination)_{10} - (Source)_{10} - X \rightarrow Destination$            | *               | U | * | U | * |  |  |  |

| S <sub>CC</sub> | Set According to Condition            | if CC then 1 $\rightarrow$ Destination; else 0 $\rightarrow$ Destination    | _               | - | - | - | - |  |  |  |

| STOP            | Load Status Register and Stop         | Immediate Data → SR; STOP                                                   | *               | * | * | * | * |  |  |  |

| SUB             | Subtract Binary                       | (Destination) – (Source) → Destination                                      | *               | * | * | * | * |  |  |  |

| SUBA            | Subtract Address                      | (Destination) – (Source) → Destination                                      | _               | _ | _ | _ | _ |  |  |  |

| SUBI            | Subtract Immediate                    | (Destination) – Immediate Data → Destination                                | *               | * | * | * | * |  |  |  |

| SUBQ            | Subtract Quick                        | (Destination) – Immediate Data → Destination                                | *               | * | * | * | * |  |  |  |

| SUBX            | Subtract with Extend                  | (Destination) – (Source) – $X \rightarrow$ Destination                      | *               | * | * | * | * |  |  |  |

| SWAP            | Swap Register Halves                  | Register [ 31:16 ] ↔ Register [ 15:0 ]                                      | _               | * | * | 0 | 0 |  |  |  |

| TAS             | Test and Set an Operand               | (Destination) Tested $\rightarrow$ CC; 1 $\rightarrow$ [ 7 ] of Destination | _               | * | * | 0 | 0 |  |  |  |

| TRAP            | Trap                                  | $PC \rightarrow SSP @ -; SR \rightarrow SSP @ -; (Vector) \rightarrow PC$   | _               | _ | _ | _ | _ |  |  |  |

| TRAPV           | Trap on Overflow                      | If V then TRAP                                                              | _               | _ | _ | _ | _ |  |  |  |

| TST             | Test and Operand                      | (Destination) Tested → CC                                                   | _               | * | * | 0 | 0 |  |  |  |

| UNLK            | Unlink                                | $An \rightarrow SP; SP @ + \rightarrow An$                                  | _               | _ | _ | _ | _ |  |  |  |

#### **Notes**

- 1. [] = bit number

- 2. \* = affected

- 3. -= unaffected

- 4. 0 = cleared

- 5. 1 = set

- 6. U = defined

- 7. @ = location addressed by

# 16-bit microcontroller

P90CE201

#### 7.1 Addressing modes

Table 16 Data addressing modes.

| MODE                                  | GENERATION                        |

|---------------------------------------|-----------------------------------|

| Register Direct Addressing            |                                   |

| Data Register Direct                  | EA = Dn                           |

| Address Register Direct               | EA = An                           |

| Absolute Data Addressing              |                                   |

| Absolute Short                        | EA = (Next Words)                 |

| Absolute Long                         | EA = (Next Two Words)             |

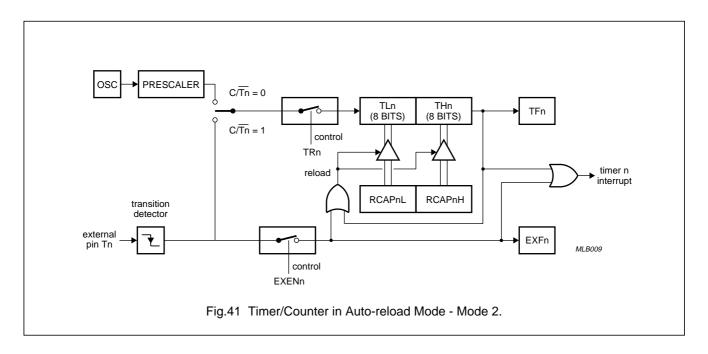

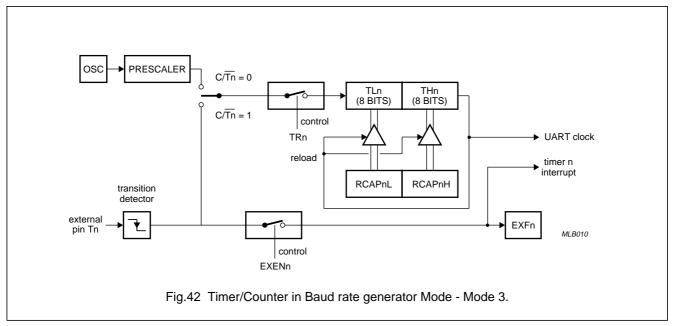

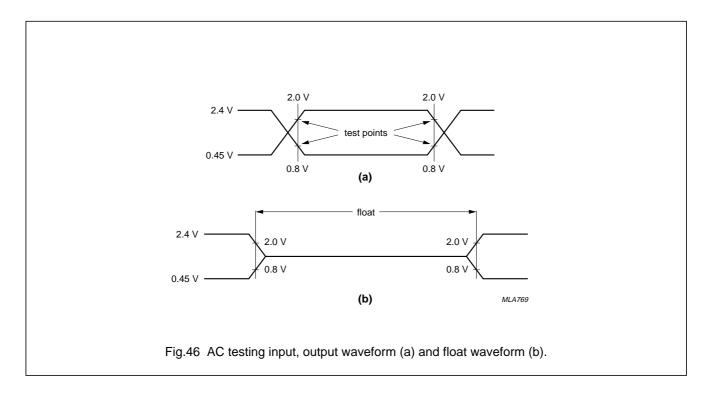

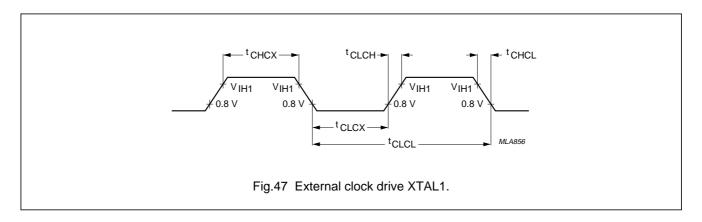

| Program Counter Relative Addressing   |                                   |